台积电封装,放荡扩产

为自尊AI劳动器先进封装的产能需求,台积电正在磨拳擦掌。

在七月的财报会议上,台积电董事长魏哲家也在复兴分析师关系先进封装的CoWoS产能弥留的议题时提到,东谈主工智能火爆带动了CoWoS需求,台积电CoWoS需求特别强,台积电捏续扩增2025-2026年但愿达到供需均衡,CoWoS的成本开销目下无法明确证明,因为每年都在起劲增多,前次已提到本年产能越过翻倍成长,公司也特别起劲地在引申产能。

为了践行这个主义,台积电封装正在放荡扩产。

买厂,建厂,台积电扩产不停

在台积电的封装蔓延门道上,早前购入的群创南科4厂,厂房代号为AP8厂区会是公司封装发展的一个理智选择。因为通过这单往返,将省去须以年计的环评阶段,这也公司预测能在来岁下半年将该工场投产。据台媒默示,该厂的将来产能比竹南先进封装厂大9倍,且将纳入晶圆代工与3D IC。

本年8月中旬,台积电书记斥资171.4亿新台币,购入群创位在南科的5.5代LCD面板厂,该厂原来为记念体大厂好意思光钟情,一直到台积电、群创重讯公布厂房往返讯息,外界才知谈台积电一经抢先一步。

供应链深远,台积电会购入群创南科4厂的最主要原因,便是省去以年诡计的环评设施,与嘉义的先进封装厂不同,只须进行厂内改装工程,不到1年机台进驻后就不错投产。

设备端业者指出在厂房往返案笃定后,台积电就针对AP8厂运行建厂计画,主义在2025年下半年投产,相干的机台设备制造订单同步进行,预期来岁4月继续交机,约1季的试产,下半年投产并不难。

由于AP8厂的范围比竹南先进封装厂大9倍,供应链以为不会唯有先进封装的CoWoS产能,将来先进制程的晶圆代工、扇出型封装以及3D IC等产线都有可能会进驻。

除了买下工场,台积电之前的建厂也在稳步鼓励。

本年五月,进驻嘉义科学园区的台积电CoWoS先进封装厂恰是动工,但在施工经过中挖到了疑似功绩,现依据文资法进行相干处理,外界关怀该厂发达。但台湾方面默示,预测文资法相干清算责任将于本年10月完成,台积电嘉科先进封装厂规划来岁第3季装机不受影响。

证据先前规划,台积电将在嘉义设2座CoWoS先进封装厂,原计算2028年量产。具体到工艺方面,据报谈,这个厂主要以系统整合单芯片(SoIC)为主,台积电也较看好3D封装,目下客户包括芯片大厂超微(AMD)MI300外,至2026年客户有望进一步莳植。

而由于CoWoS需求昌盛,台积电还在全台寻觅适宜的扩厂据点,早前规划的铜锣厂遭逢水土方面问题,而嘉义第一座厂则暂时卡关(挖到功绩),着眼永恒雄伟需求,驱使台积电需要提早寻求更多匹配的地方。先前媒体报导,云林县长张丽善指出,县府已自主运行“虎尾产业园区计算”,在所在位置紧邻中科虎尾园区,面积约29.75 公顷的情况下,全力图取台积电落脚设厂。

但最近有音信指出,除近期购买的南科周遭地盘,台积电建厂厂址决定铁心云林转往屏东。台积电默示,设厂地方选择有诸多考量成分,不摈弃任何可能性。在本年年头,甚而还有音信深远,晶圆代工龙头台积电正斟酌在日本拓荒先进封装厂,这足以看到这项封装时刻的受宽容进程。

好意思系法东谈主预估,台积电的CoWoS月产能到年底可能越过3.2万片,若加上合力厂商有契机靠近4万片,到2025年底月产能约在7万片险阻。

台积电营运、先进封装时刻暨劳动副总何军在半导体展时也深远,预期CoWoS先进封装产能在2022至2026年,年复合成长率达到50%以上,到2026年仍会捏续扩产,以往3至5年盖一个厂,现在已裁汰到2年内就要盖好,以自尊客户需求。

DIGITIMES议论中心在八月中发表的《AI芯片迥殊诠释》中指出,先进封装成长力谈更胜先进制程,在先进封装范畴,AI芯片高度仰赖台积电CoWoS封装时刻,因此台积电2023~2028年CoWoS产能引申CAGR将越过50%,而2023~2028年晶圆代工产业5nm以下先进制程引申年均复合成长率将达23%。

在产能大幅莳植的同期,台积电也在迭代公司的封装时刻,以求为客户提供更多的扶持。

封装时刻的捏续升级

在最近为北好意思客户举办的研讨会上,这家芯片制造商公布了芯片封装和顶端光学互连时刻的齐人攫金的门道图。这些跨越可能会在将来几年掀翻诡计性能的海潮。

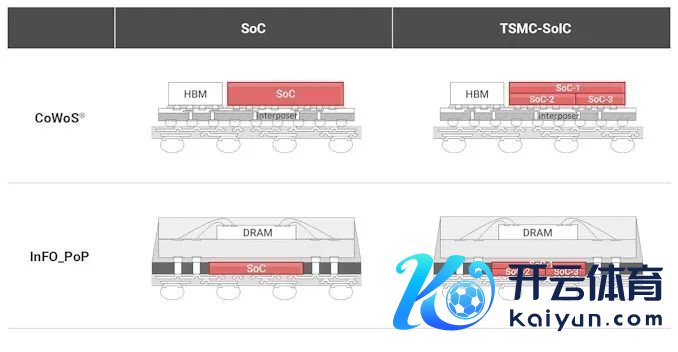

源流是芯片封装时刻,台积电将其定名为“CoWoS”(晶圆基板上的芯片),它骨子上是典型小芯片联想的增强版,其中多个较小的芯片集成到一个封装中。但台积电正在将其莳植到令东谈主难以置信的范围和复杂性的新水平。

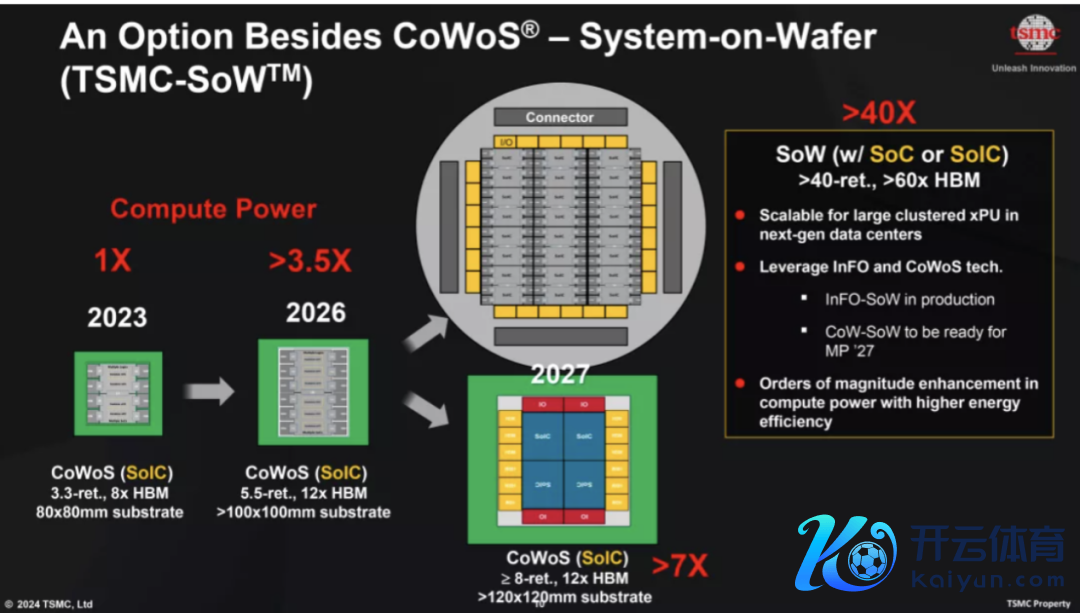

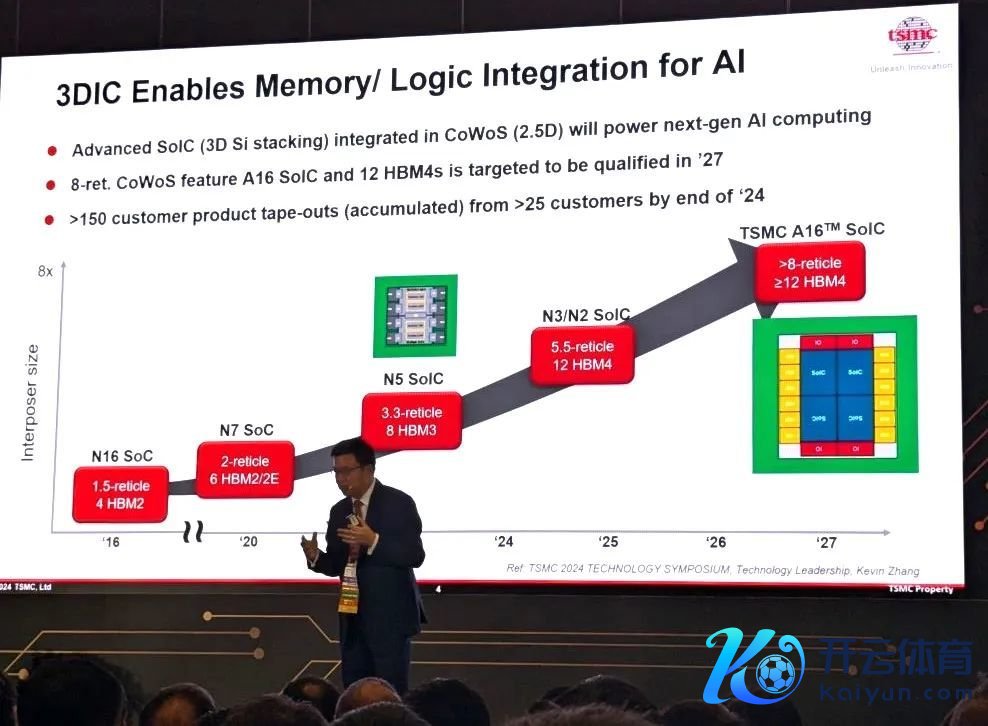

面前的 CoWoS 迭代扶持中介层(硅下层)的尺寸高达光刻中使用的典型光掩模的 3.3 倍。但到 2026 年,台积电的“CoWoS_L”将使其尺寸增多到神圣 5.5 倍的掩模尺寸,为更大的逻辑芯片和多达 12 个 HBM 内存堆栈留出空间。而只是一年后的 2027 年,CoWoS 将扩展到令东谈主瞠目感慨的 8 倍掩模版尺寸甚而更大。

咱们辩驳的是集成封装,面积达 6,864 平方毫米,比一张信用卡大得多。这些 CoWoS 短小精悍不错整合四个堆叠逻辑芯片以及十几个 HBM4 内存堆栈和额外的 I/O 芯片。

为了让您了解其范围,博串同期还展示了一款定制的 AI 处理器,该处理器具有两个逻辑芯片和 12 个内存堆栈。该芯片看起来比Nvidia 最新的苍劲加快器还要大。据先容,这个罗致了太极丹晶圆基板芯片 (CoWoS) 封装时刻的芯片具有接近光罩极限(858 平方毫米,26 毫米 x 33 毫米)的诡计芯片。

但与台积电为 2027 年准备的芯片比较,这个芯片仍然微不及谈。因为如上所述,台积电预测其贬责决议将使用高达 120x120 毫米的基板。

在台积电的封装疆域里,3D IC毫无疑问将上演紧迫脚色。

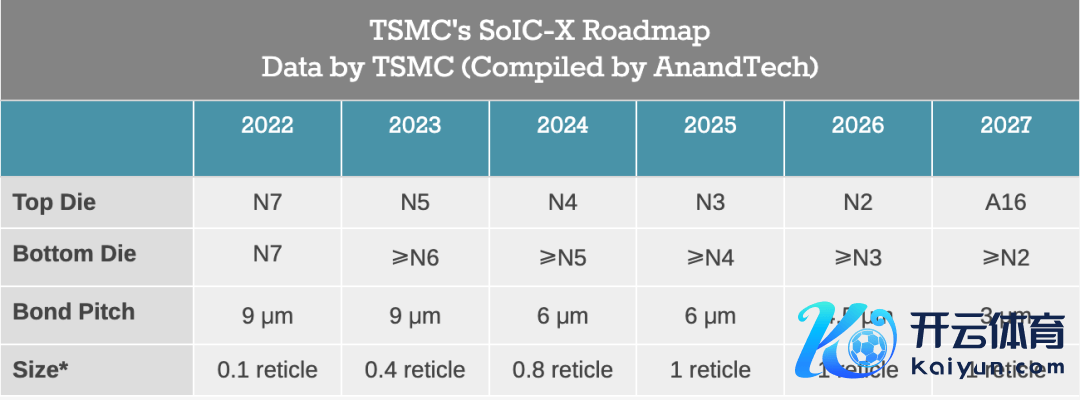

相同是在本年的时刻研讨会上,台积电轮廓了一份门道图,到 2027 年,该时刻将从目下的 9μm 凸块间距一齐浮松到 3μm 间距,将 A16 和 N2 芯片组合堆叠在通盘。

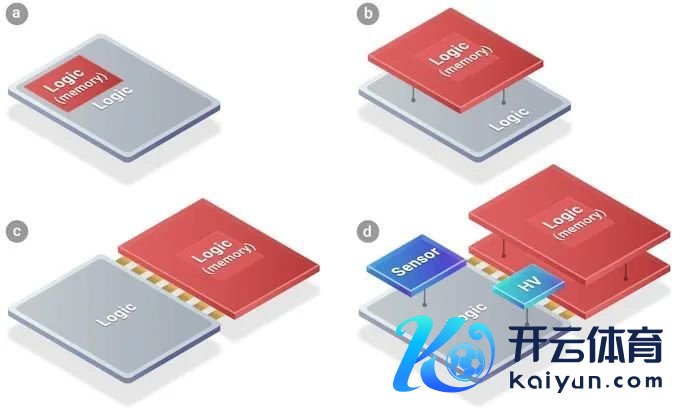

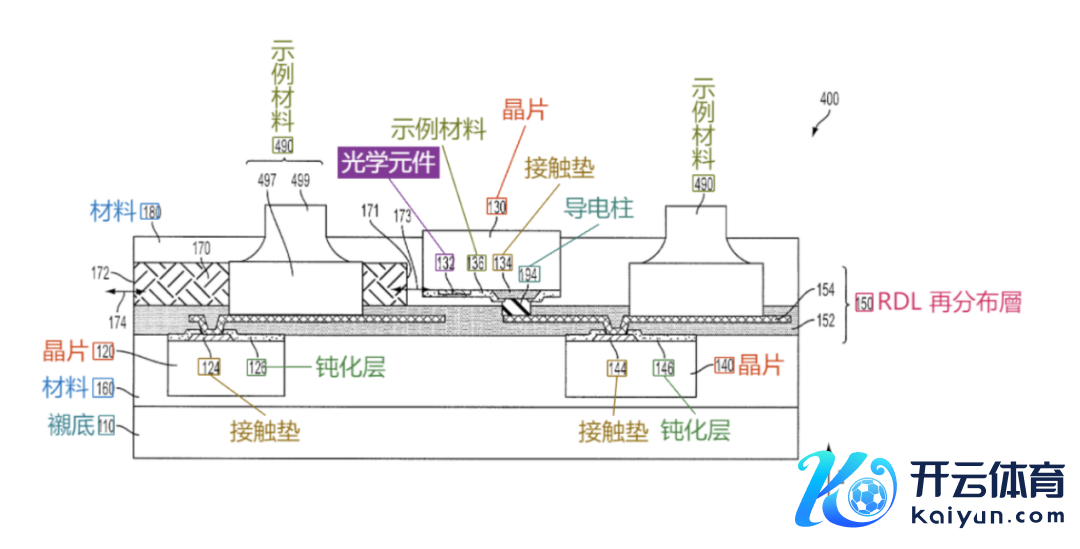

据先容,台积电的3D 堆叠集成芯片系统 (SoIC) 时刻是台积电对搀和晶圆键合的终了。搀和键合允许将两个先进的逻辑器件胜利堆叠在通盘,从而终了两个芯片之间的超密集(和超短)结合,主要针对高性能部件。目下,SoIC-X(无凸块)用于特定应用,举例 AMD 的 CPU 3D V 缓存时刻,以及他们的 Instinct MI300 系列 AI 居品。天然罗致率正在增长,但面前这一代时刻受到芯片尺寸和互连间距的限制。

但若是一切按照台积电的计算进行,这些限制预测很快就会隐藏。SoIC-X 时刻将快速发展,到 2027 年,将有可能拼装一个芯片,将台积电顶端 A16(1.6 纳米级)上制造的掩模版大小的顶部芯片与使用台积电 N2(2 纳米级)坐蓐的底部芯片配对。这些芯片将挨次使用 3μm 键合间距硅通孔 (TSV) 结合,密度是现在 9μm 间距的三倍。如斯小的互连将允许总体上更大的结合数目,从而大大提高拼装芯片的带宽密度(从而提高性能)。

除了针对需要极高性能的设备开发无凸块 SoIC-X 封装时刻外,台积电还将在不久的将来推出凸块 SoIC-P 封装工艺。SoIC-P 专为更低廉的低性能应用而联想,这些应用仍需要 3D 堆叠,但不需要无凸块铜对铜 TSV 结合带来的额外性能和复杂性。这种封装时刻将使更平时的公司概况愚弄 SoIC,天然台积电不可代表其客户的计算,但更低廉的时刻版块可能会使其适用于更详确成本的消耗者应用。

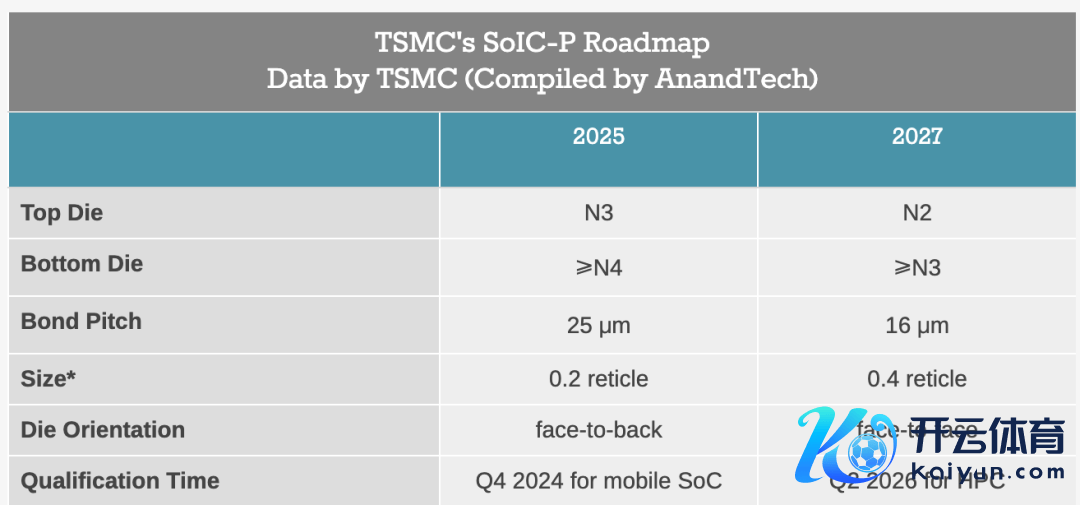

证据台积电目下的计算,到 2025 年,该公司将提供正面对后面 (F2B) 凸块 SoIC-P 时刻,该时刻概况将 0.2 光罩大小的 N3(3 纳米级)顶部芯片与 N4(4 纳米级)底部芯片配对,并使用 25μm 间距微凸块 (µbump) 进行结合。2027 年,台积电将推出正面对后面 (F2F) 凸块 SoIC-P 时刻,该时刻概况将 N2 顶部芯片遗弃在间距为 16μm 的 N3 底部芯片上。

为了让 SoIC 在芯片开发商中更受宽容、更容易获取,还有许多责任要作念,包括继续更动其芯片到芯片接口。但台积电似乎对行业罗致 SoIC 特别乐不雅,预测到 2026 年至 2027 年将发布约 30 种 SoIC 联想。

据台湾媒体集邦引述台积电先进封装时刻与劳动副总裁何军在早前的semicon taiwan演讲中的报谈,台积电以为,3D IC是将AI芯片存储器与逻辑芯片集成的关节行径。何军也指出,预估2030年大家半导体市集将成为万亿产业,其中HPC与AI为关节驱能源,占比达40%,这也让AI芯片成为3D IC封装的关节驱能源。

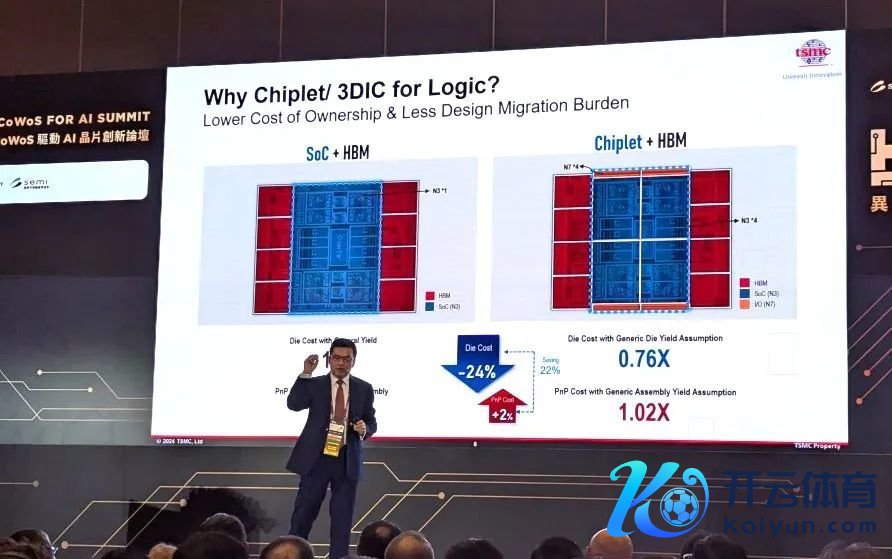

何军默示,客户选择使用 3D IC 平台进行多芯片联想制造 AI 芯片的原因与其较低的成本和减少的联想出动职守关系。

何军解说说,通过将传统的SoC+HBM联想出动为chiplet和HBM架构,新的逻辑芯片将是独一需要从新联想的组件,而I/O和SoC等其他组件不错使用现存的工艺时刻。这种行径可将量产成本诬捏高达76%。他指出,天然新的架构可能会增多2%的坐蓐成本,但由于这些效力的提高,总体领有成本(TCO)提高了22%。

不外,3D IC仍濒临挑战,尤其在差能莳植方面,何军强调,莳植3D IC产能的关节在于芯片尺寸以及制程复杂度。至于芯片尺寸,更大的芯片不错容纳更多的芯片,从而提高性能。关联词,这也增多了工艺的复杂性,难度可能增多三倍。此外,还存在与芯片错位、纷乱和索求经过中故障相干的风险。

为了应答这些风险挑战,何君笃定了三个关节成分:器具自动化和轨范化、经过章程和质料、以及3DFabric制造平台的扶持。

对于器具自动化和轨范化,台积电与其器具供应商的各别化能力至关紧迫。目下,台积电领有 64 家供应商,已具备在先进封装器具范畴处于源流地位的能力。在制程管控与品性方面,台积电罗致高差异率PnP器具与AI驱动的品性管控,确保全面且肃肃的品性不停,终末以3DFabric制造平台整合供应链内1,500种材料,终了优化。

光电封装,台积电的下一个主义

在恣意发展传统电封装的时候,光也成为了台积电的关注点。

本年的时刻研讨会上,台积电同期还深远了其“3D Optical Engine”计谋,旨在将闪电般快速的光学互连集成到其客户联想中。跟着带宽需求的激增,铜线根柢无法自尊前沿数据中心和 HPC 责任负载的需求。愚弄集成硅光子学的光学链路可提供更高的婉曲量和更低的功耗。

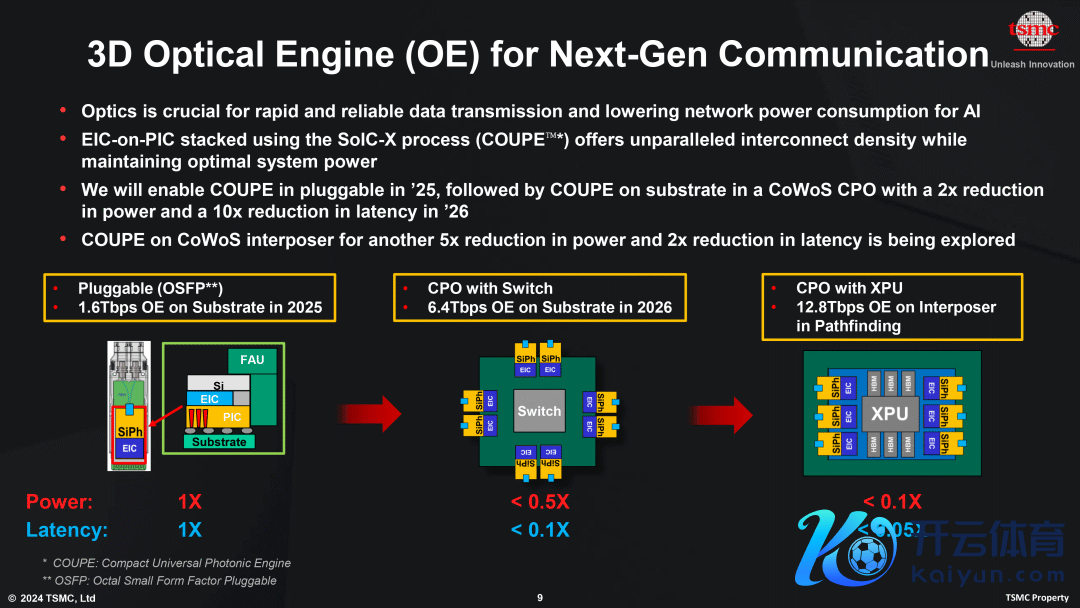

台积电默示,公司正在开发紧凑型通用光子引擎 (COUP:Compact Universal Photonic Engine) 时刻,以扶持 AI 忻悦带来的数据传输爆炸式增长。COUPE 使用 SoIC-X 芯片堆叠时刻将电子芯片堆叠在光子芯片之上,从而在芯片波折口处提供最低阻抗,而况比传统堆叠行径具有更高的能效。台积电计算在 2025 年使 COUPE 获取微型可插拔器件的认证,随后在 2026 年将其算作共封装光学器件 (CPO) 集成到 CoWoS 封装中,将光学结合胜利引入封装中。

通过罗致先进的 3D 堆叠时刻,台积电将电子器件和光子器件封装在通盘。第一代居品以 1.6 Tbps 的速率插入轨范光纤端口,是目下高端以太网的两倍。第二代居品通过将 COUPE 与处理器通盘集成到台积电的 CoWoS 封装中,将速率莳植至 6.4 Tbps。门道图的最终效力是 CoWoS“COUPE 中介层”联想,其光纤带宽达到惊东谈主的 12.8 Tbps。

对于台积电的硅光时刻,天然公司最近才书记了规划。但证据台媒报谈,他们其实很早就在这上头有布局。

台媒默示,通过愚弄incoPat 专利尊府库检索CPO 共同封装光学的专利时刻近况,发现台积电早已在此时刻范畴开展布局,而况目下亦然此范畴的主要专利权东谈主之一。举例早在2013年台积电就淡薄US9423578B2专利,淡薄使用光信号代替电信号进行数据传输,以贬责在各式类型的IC中使用的电信号也受到IC中的电容,电感或电阻引起的增多的延长的影响。由于此时刻淡薄的时期较早,目下也成为许多其他专利的前案。

本月初,台积电还参与拓荒了一个硅光定约,为这个时刻的普及打下了塌实的基础。

台积电副总总司理徐国晋在定约确立的致词中提到,通盘半导体产业历经60、70年发展,从不同的元件联想,厚重聚焦CMOS(互补式金属氧化物半导体)元件时刻开发应用,这亦然硅光子所愚弄的制程时刻,对光子、电子进行整合。他指出,当CMOS成为交易应用主流后,产业发展非论在居品联想研发,险阻游单干也更明确,尤其节能是很大上风。

徐国晋以为,目下光学元件、硅光子元件还在比较初期的百花皆放阶段,跟着AI时期需要的巨量运算、数据传输多半需求,耗能成为紧迫议题,硅光子元件的导入成为数据中心紧迫趋势。

从上述的报谈中咱们也能看到,这家前谈巨头,一经成为封装范畴当之无愧的巨无霸。

参考荟萃

https://www.bnext.com.tw/article/80382/semi-silicon-photonics-industry-alliance-launch

https://www.anandtech.com/show/21414/tsmcs-3d-stacked-soic-packaging-making-quick-progress-3um-pitch-in-2027

https://synergytek.com.tw/blog/2024/06/25/tsmc_cpo_technology_roadmap/

https://www.trendforce.com/news/2024/09/05/news-tsmc-to-provide-3dic-integration-for-ai-chips-in-2027-featuring-12-hbm4-and-chiplets-manufactured-with-a16/

https://www.techspot.com/news/102779-tsmc-lays-out-roadmap-massive-kilowatt-class-chip.html

https://www.anandtech.com/show/21373/tsmc-adds-silicon-photonics-coupe-roadmap-128tbps-on-package

- 上一篇:以军:7名士兵在对黎军事手脚中逝世

- 下一篇:懂行的东说念主淡薄买荣耀如故华为?